http://www.asyura2.com/17/hasan121/msg/116.html

| Tweet |

東芝メモリ喫緊の課題「3次元NAND」、サムスンの独走許した深い理由 業界が驚いたiPhone7の3次元NAND

http://wedge.ismedia.jp/articles/-/9373

2017年4月14日 湯之上 隆 (微細加工研究所所長) WEDGE Infinity

3次元NANDで周回遅れとなった東芝

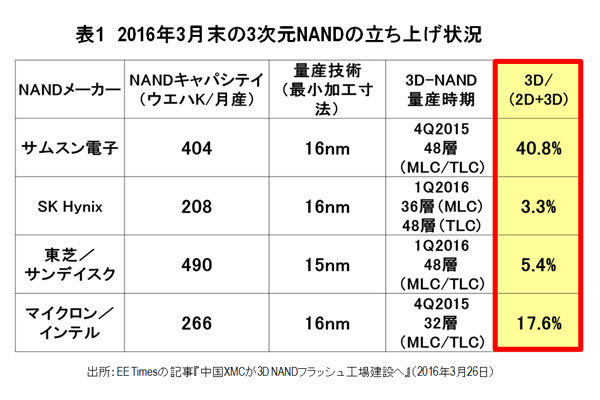

米半導体業界誌EE Timesの2016年3月26日の記事に、世界に4グループあるNANDメーカーにおける3次元NANDの立ち上げ状況を示すデータが掲載された(表1)。それは、衝撃的だった。

表1によれば、サムスン電子のNANDの生産キャパシティは月産ウエハ枚数40.4万枚で、2015年第4四半期に48層の3次元NANDの量産を開始し、2016年3月時点では全キャパ内の40.8%で3次元NANDを生産していることになる。

一方、東芝&サンディスクは、2016年第1四半期から48層の3次元NANDの生産を開始しているが、月産49万枚のキャパの内、3次元NANDに使われているのは、たった5.4%しかない。これは、SK Hynixの3.3%よりましだが、マイクロン&インテルの17.6%の1/3以下である。

NANDは1987年に東芝が発明した半導体メモリであり、2007年に世界に先駆けて3次元NANDの学会発表を行ったのも東芝である。にもかかわらず、なぜ、その量産でサムスン電子にこれほどまで差をつけられてしまったのか。

本稿では、その第1の原因が3次元NANDの途轍もなく難しい深孔加工技術にあったことを述べる。また、第2の原因として、サムスン電子が3次元NAND工場を中国の西安に建設したことも影響していることを論じる。

2次元NANDと3次元NANDの比較

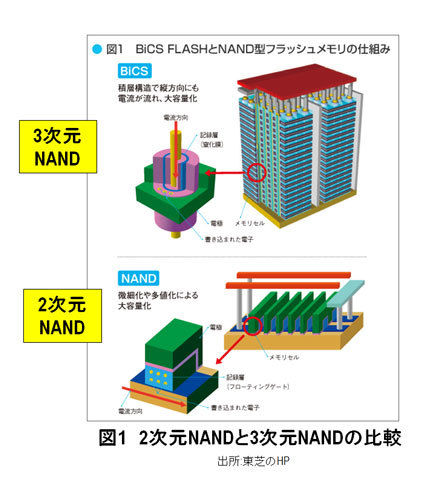

第2回のコラムで、2次元NANDを微細化していくと、15〜16nm付近からメモリセル同士の干渉(クロストーク)が起きるため、メモリセルを縦方向に積む3次元化が考案されたと説明した。

東芝のHPに掲載されている2次元と3次元(BiCS)の比較図を見てみよう(図1)。尚、BiCSとは、Bit Cost Scalableの略で、東芝の3次元NANDの呼称である(一方、サムスン電子は、Vertical-NAND(V-NAND)と呼称している)。

2次元が江戸時代に存在した庶民用住居の“長屋”のような構造であるのに対し、3次元は超高層マンションのような構造となっていることがわかる。前節で「サムスン電子が48層の3次元NANDを量産開始」とかいたが、この「48層」とは、縦方向にメモリセルが48個積層していることを意味する。要するに、48階建てのマンションと思って頂ければいいだろう。そして、積層数が高いほど、単位面積辺りのメモリセル密度が大きくなるため、NANDメーカーは、どれだけ積層できるかという競争をしているわけだ。

3次元NANDのメモリセルのつくり方

この高層マンションのような3次元NANDのメモリセルはどうやってつくるのか。東芝のHPに簡単な製造方法が書いてあるので、これを元に説明する(図2)。

例えば48層の3次元NANDをつくる場合、まず、シリコン酸化膜(SiO2)などの絶縁膜を48層積層する。次に、48層積層された膜を縦に貫通する微細な孔を形成する。最後に、この孔をタングステン(W)などの金属で埋め込む。本当はもっと複雑なのだが、本稿では深入りせずに、「膜を積んで、孔をあけて、金属で埋め込む」程度にとどめておく。

最も難しいのは深孔加工

この中で特に難しいのが、ドライエッチングと呼ばれる技術を使って、微細で深い孔をあける工程である。東芝のIR資料の中に、その難しさを直感的に理解するのにちょうど良い図があったのでそれを基に説明しよう(図3)。これは、東芝の64層の3次元NANDの模式図(左側)と断面顕微鏡写真(右側)を示している。

右側の写真のように縦方向に64層のメモリセルを形成するには、直径100nmで深さ4.5μm(4500nm)の孔を開けなければならない。孔の深さと直径の比をアスペクト比と呼んでいるが、この3次元NANDでは、アスペクト比45:1の孔をあける必要があるわけだ。この孔のアスペクト比は、高さ634mで底辺68mの東京スカイツリー5棟分に相当すると東芝は説明している。そして、このような超高アスペクト比の孔を12インチウエハ上に1兆7000個も同時に開けなければならないのである。

かつて筆者は日立やエルピーダで、DRAMというNANDとはちょっとタイプの違う半導体メモリのドライエッチングを担当していた。2000年頃に、当時最先端だった64MビットDRAMのキャパシタ用の深孔を「もう限界だ、もう無理だ」とヒイヒイ言いながら加工していたことを記憶しているが、そのアスペクト比は、たったの12:1だった。

そして現在、最先端のDRAMは4Gビットであるが、そのキャパシタ用の深孔のアスペクト比せいぜい20〜25程度である。DRAMでは、この深孔の加工が非常に難しいため、微細化がスローダウンしており、半導体デバイスの中ではもっとも早く微細化の終焉が来ると言われているほどである。

ところが、3次元NANDでは、アスペクト比45:1の孔を開けなければならないのである。しかも、今後、積層数が増大するため、より深い孔をあける必要に迫られており、そのアスペクト比は60:1〜80:1になりつつある。

アスペクト比12:1の孔をあけるのに苦労していた筆者としては、正直なところ、「3次元NANDの深孔加工担当のドライエッチング技術者でなくてよかった」と思うほどである。東芝もサムスン電子もマイクロンもSK Hynixも、3次元NANDの深孔加工担当者には、同情を禁じ得ない。

東芝の迷走の始まり

半導体史上もっとも困難な深孔加工を強いられる3次元NANDの製造であるが、この深孔加工を巡って東芝は迷走に次ぐ迷走を重ねた。

当初、東芝の積層膜は、シリコン酸化膜(SiO2)/多結晶シリコン(PolySi)/シリコン酸化膜(SiO2)/多結晶シリコン(PolySi)/…という構造だった。これを「OPOP構造」と呼んだ。この構造で、深孔加工を行おうとしたが、孔は開かなかった。というのは、絶縁膜のSiO2と導電膜のPolySiでは、ドライエッチング条件がまったく違うからである。通常は、絶縁膜(SiO2)用と、導電膜(PolySi)用に、専用のドライエッチング装置を使ってまったく異なる条件で加工している。それを一括して孔を開けようというのは、土台無理な話だったわけだ。

そこで東芝は、サムスン電子が採用していたシリコン酸化膜(SiO2)/シリコン窒化膜(SiN)/シリコン酸化膜(SiO2)/シリコン窒化膜(SiN)/…という構造を模倣した(要するにパクった)。これを「SNSN構造」という。シリコン窒化膜(SiN)は、シリコン酸化膜(SiO2)と同じ絶縁膜に分類されるので、この構造なら同じ装置での一括加工が可能になる。

実は、サムスン電子がNANDにいち早く採用した「SNSN構造」も、サムスン電子が開発したものではなく、米スパンションのNORフラッシュという半導体メモリの構造を模倣した(要するにパクった)ものである。また東芝の技術者曰く、「湯之上の言うことは正確ではない。東芝は、サムスン電子をパクったSK Hynixをパクったのだ」。半導体業界というのは、このようにパクり合戦を行っているのだが、この辺りの経緯は、第4回のコラムで詳述する。

まだまだ続くよ迷走は

東芝は、3次元NANDの構造で迷走したが、装置選定でも迷走した。ドライエッチング装置メーカーには、米ラムリサーチ、米アプライドマテリアルズ、東京エレクトロン、日立ハイテクノロジーズの4社がある。この中で、3次元NANDの深孔加工は、ラムリサーチがほぼ独占している。

ところが、東芝は東京エレクトロンとのつながりが非常に深い。そこで、まず、東京エレクトロンと深孔加工用のドライエッチング装置を共同開発した。しかし、その装置では深孔は開かなかった(正確に言うと、ウエハ数枚くらいは加工できるかもしれないが、連続着工性に問題があり、量産装置には適用できなかった)。

そこで、東芝のドライエッチング部隊は、ラムリサーチとアプライドの装置を評価し、ラムリサーチを選定して購入することにした。

ところが、資材課が購入したのは、技術部隊が選定したラムリサーチ製ではなく、選定しなかったはずのアプライド製だった! なぜこんな不思議なことが起きたのか?

その理由は、次の通りである。東芝の資材課には、技術者から移籍してくる者がいる。私だったら、技術グループから資材課へ行けと命じられたら、「左遷された」と思うかもしれない。しかし、どうも東芝には、技術者→資材→幹部というような出世ルートがあるらしい(不正会計が発覚して辞任に追い込まれたときの社長の田中久雄氏も調達出身だった)。

そして、このときドライエッチング部隊からの要請で装置を購入する担当となった者が、元ドライエッチング技術者だったらしい。ドライエッチングの世界にいる(いた)者ならば、次のようなことを良く知っている。

ラムリサーチとアプライドの間は、人の行き来が激しい。実際、ラムリサーチで装置設計を行った人物が、アプライドに行って装置設計を行ったりしている。その結果、両社の装置は、似たような構造になっている(同じ人間が設計しているのだから似るのは当たり前だ)。

このことを知っていた元ドライエッチング技術者の資材担当者は、両社に相見積を取った。ここまでは、資材担当者としては当然やるべき仕事をやったに過ぎない。ところが、見積もった結果、ラムリサーチよりアプライドの方が3割ほど安かったらしい。そして、「同じような装置なのだから」という理由で、安い方のアプライドを買ってしまったというわけである。

東芝のドライエッチング部隊はさぞや驚いたことだろう。選定した装置とは違うものが購入されてきたたわけだから。しかし、東芝のドライエッチング部隊は、選定しなかった(性能が悪い方の)装置を使って孔を開けようと奮闘するのである。しかし、やはり孔は開かなかった。

最後の迷走

その結果、アプライドの装置を断念し、やっと、念願のラムリサーチのドライエッチング装置を導入することになった。やっと一件落着かと思いきや、最後の迷走が待っていた。

ラムリサーチのドライエッチング技術には、深い孔を開けるために、ちょっと特殊なガスを添加することにミソがあった。ところが、東芝は二つの理由で、そのガスを使うことを拒否したのである。

まず第一に、半導体工場では、製造装置へのガスの供給は集中配管システムを採用しているため、ボンベを転がしてきて装置にくっ付ければいいという訳にはいかないのである。

第二に(これが問題なのだが)、東芝の技術者は根拠のない自信を持っているせいで、「そんな特殊なガスを使わなくても孔を開けてみせる」と言い張った。

ところが、やはり孔は開かなかった。その結果、ラムリサーチ推奨のガスを使うことになり、半導体工場における集中配管システムの工事が行われるに至るわけだ。

こうして東芝の迷走を綴ってみると、素直に最初からラムリサーチのドライエッチング装置を買い、ラムリサーチの言う通りのガスを使っていればと、思わずにはいられない。東芝はまるで、「我に艱難辛苦を与えよ」とでも思って自らドツボに陥っているとしか思えないのである。そして、徒に時間だけが過ぎていく。

東芝が周回遅れになったもう一つの事情

ここまで、3次元NANDで東芝が周回遅れになった理由が、深孔加工で迷走したことにあったことを詳述した。ところが、例え、深孔加工がすんなりできたとしても、東芝には48層の3次元NANDを大量生産できない事情があった。

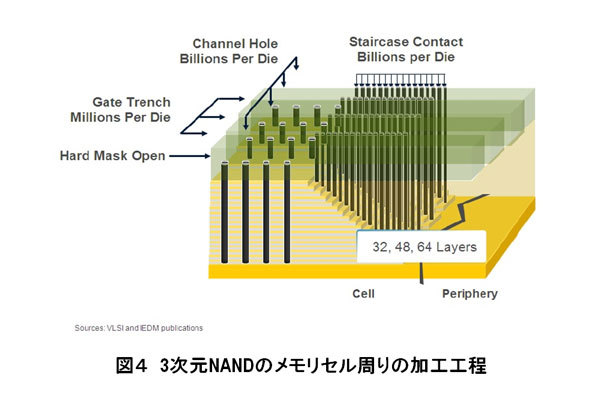

その事情とは次の通りである。3次元NANDの製造には、2次元NANDよりも、製造コストが2〜3割高くなる。それは、図2に示したように、3次元NANDの製造には、膜を積み、深孔を開ける工程に装置が大量に必要になるからである。

例えば、東芝が迷走したメモリセルの深孔のドライエッチングでは、ラムリサーチの装置を使っても、1時間に1枚しか処理できない。因みに、2次元NANDのメモリセルでは、このような孔の加工は僅か1〜2分で済む。

半導体メモリの量産工場では、1ヶ月にウエハを約10万枚流す。30日で10万枚だから、1日あたり3333枚の処理が必要となる。1ロット25枚入りのカセットで計算すれば、1日あたり133ロットの処理が必要となる。

ところが、メモリセルの深孔は、1枚1時間かかる。1チャンバで1日に1ロット(25枚)程度しか処理できない。したがって、1日に133ロット処理するためには、最低133チャンバのドライエッチング装置が必要となる。メンテナンスなどの余裕をみれば150〜200チャンバ程度は必要だ。

さらに、メモリセル周りには、深孔加工以外にも、深孔加工の前のハードマスク加工、スリット(溝)加工、階段状のホール加工が必要となる。それを全部合計すると、恐らくメモリセル周りだけで400〜500チャンバ位必要になるのではないか。

このように3次元NANDには、2次元NANDに比べて桁違いな装置台数が必要となる。その結果、試算すると、48層まではつくっても利益が期待できないのである。したがって、業界では、3次元NANDの勝負は64層からになると思われていた。

実際、表1を見せて、「何で東芝は生産キャパの5.4%しか3次元NANDをつっていないのか?」と聞くと、東芝関係者は、「48層まではつくればつくるほど赤字だ。だから東芝は次(64層以降)にアクセルを踏む」という見解を示した。

なぜサムスン電子は48層で大量生産に踏み切ったのか

表1に示されている通り、2016年3月時点で、サムスン電子は48層の3次元NANDを大量生産しており、その割合は40.8%を占める。東芝関係者の言う通りなら、サムスン電子は大赤字になっているはずだが、実際はそうではないようだ。

2016年3月当時、サムスン電子は、2次元NANDは韓国工場で製造し、3次元NANDは中国の西安工場で量産していた。中国の半導体事情に詳しい識者によれば、「中国が招致した西安工場では、土地代がタダ、電気や水などのインフラ代がタダ、法人税が向こう10年間免除、加えて、オペレーターとして現地中国人を2千人規模で採用しているため各種補助金が出る。そのため税引前利益では(東芝関係者が言うように)赤字かもしれないが、税引後利益では黒字になっている」というのである。

つまり、サムスン電子は、中国の立地上の優位性を利用して、競合他社が踏み切れなかった48層の3次元NANDをいち早く大量生産できたということである。そして、サムスン電子は東芝を含む競合他社を大きく引き離すとともに、3次元NANDの製造ノウハウをどこよりも速く手に入れることにもなった。

歩留り向上とともに技術も向上

半導体には、歩留りというパラメータがある。例えば、12インチウエハに1000個の3次元NANDをつくる場合、そのうち良品が800個取れたら、歩留り80%ということになる。通常、半導体メモリでは、80〜90%以上の歩留りにならないと、利益が出ない。

ところが、開発センターで500〜1000工程程になるプロセスフローが確定して、これが量産工場に移管された際、歩留りはゼロに近い。歩留りゼロから少しずつウエハ投入量を増やしていき、500〜1000工程のプロセス一つ一つを最適化していくことによって、歩留りは向上していく。

その過程で、工程フローをつくりかえることもあるし、場合によっては開発センターに差し戻されて、設計からやり直す場合もある。このような一連の改善作業を通じて、半導体メーカーは、その製品の勘所を学習し、ノウハウを蓄積していく。

つまり、ウエハを流す→改善する→もっとウエハを流す→もっと改善する、というサイクルを繰り返すことにより、歩留りが80〜90%に向上し、それに伴って、半導体メーカーはノウハウや技術を蓄積していくのである。

48層の3次元NANDの大量生産にいち早く踏み切ったサムスン電子は、最先端品を何処よりも早く市場に投入したことによる利益を得るとともに、3次元NANDの製造ノウハウや技術も蓄積したわけである。

遅ればせながら東芝も3次元NANDを製造

3次元NANDの構造、深孔加工、48層の量産、これらすべてにおいて、サムスン電子に比べて東芝は周回遅れとなった。

ところが、昨年発売されたアップル社のiPhone7の最高級機種を分解したら、東芝製の48層3次元NANDが出てきたのである。スマホに3次元NANDが使われたのは、恐らくこれが初めてのケースであろう。そして、サムスン電子ではなく東芝製だったことに、業界は驚いた。遅ればせながら、東芝も3次元NANDを量産し始めたわけである。

しかし、これは48層であり、東芝関係者が言っていたように、これを量産し続けても利益は出ない。そこで東芝は、2017年2月に、64層3次元NANDのサンプル出荷を開始したと発表した。これは東芝が勝負をかけている製品である。ここでアクセルを全開にして、大量生産を行い、ノウハウを蓄積し、技術の向上も図る。

サムスン電子、東芝&ウエスタンデジタル(サンディスク)、マイクロン&インテル、SK Hynix、これら4グループが、64層およびそれ以上の積層数の3次元NANDの開発と量産で火花を散らす。ところが、この4グループの争いに、中国の紫光集団傘下のXMCが参入することとなった。第4回は、このXMCについて詳述したい。

|

|

|

|

投稿コメント全ログ コメント即時配信 スレ建て依頼 削除コメント確認方法

▲上へ ★阿修羅♪ > 経世済民121掲示板 次へ 前へ

|

|

スパムメールの中から見つけ出すためにメールのタイトルには必ず「阿修羅さんへ」と記述してください。

スパムメールの中から見つけ出すためにメールのタイトルには必ず「阿修羅さんへ」と記述してください。すべてのページの引用、転載、リンクを許可します。確認メールは不要です。引用元リンクを表示してください。