| Tweet |

http://techon.nikkeibp.co.jp/article/NEWS/20070211/127607/

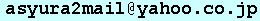

タイル1個を21の電力管理の区画に分割。写真ではそのうちの5区画とスリープ時の電力削減効果を示している。

米Intel Corp.は2007年2月11日,半導体技術の国際学会「Integrated Solid State Circuits Conference (ISSCC)2007」(2007年2月11~15日,米国サンフランシスコ市)の開催に合わせて,80個のCPUコアを1チップ上に集積したマイクロプロセサの試作チップの性能のいくつかを発表した。同社が2006年9月の「Intel Developer Forum(IDF)Fall 2006」で初公開した同チップの消費電力や設計の詳細を明らかにしたもの(関連記事)。

具体的には,電源電圧0.95V,動作周波数3.16GHzの場合に演算性能は1.01TFLOPS,消費電力は62Wであるという。現在のデュアル・コア型86系マイクロプロセサが消費電力60~100Wで10G~20GFLOPSであることから,今回のチップは単位消費電力当たりの演算性能は50倍以上になる。東京大学と国立天文台が2006年11月に発表したプログラム可能なアクセラレータLSI「GRAPE-DR」の,60Wで 512GFLOPSと比較しても約2倍,電力効率が高い。

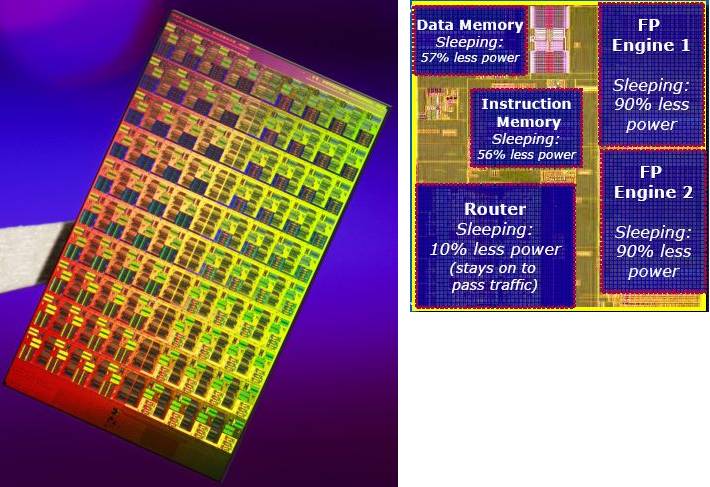

今回のマイクロプロセサはチップ全体で1億個のトランジスタが集積されている。チップは「タイル」と呼ぶ80個の区画に分かれる。タイル1個中には浮動小数点演算ユニット2個と「ルーター」と呼ぶスイッチ回路,およびデータ用メモリと命令セット用メモリなどが搭載されている。ルーターは,隣接する 4個のタイルとの接続用に4個,さらにコアに張り合わせる「3D積層メモリ」(Intel社)と呼ぶSRAMを接続するための1個の計5個の入出力ポートを備え,総データ転送容量は80Gビット/秒である。なお,3D積層メモリの詳細については触れていない。

消費電力の効率を大きく高めることにつながった技術としてIntel社は「Fine Grain Power Management」技術をあげる。これは,各タイルをそれぞれ21の電力管理の区画に分け,電力を区画ごとに制御する技術である。

同社は,今回のチップで5.7GHzにまで動作周波数を高めた場合の性能も発表した。その場合の電源電圧は1.35V,演算性能は1.81TFLOPSと非常に高いが,消費電力は265Wと3.16GHz動作の時の4倍超になってしまうという。

さらに技術的な詳細は,2月12日(現地時間)にISSCC 2007で報告するという。

投稿コメント全ログ コメント即時配信 スレ建て依頼 削除コメント確認方法

題名には必ず「阿修羅さんへ」と記述してください。

題名には必ず「阿修羅さんへ」と記述してください。

掲示板,MLを含むこのサイトすべての

一切の引用、転載、リンクを許可いたします。確認メールは不要です。

引用元リンクを表示してください。